# Accurate analysis of real-time stream processing applications

using dataflow models and timed automata

Guus Kuiper

Members of the graduation committee:

| Prof. dr. ir.  | M. J. G. Bekooij | University of Twente (promotor)               |

|----------------|------------------|-----------------------------------------------|

| Prof. dr. ir.  | G. J. M. Smit    | University of Twente                          |

| Dr.            | A. K. I. Remke   | University of Twente                          |

| Prof. dr. ing. | J. Castrillon    | Technische Universität Dresden                |

| Prof. dr. ir.  | T. Basten        | Eindhoven University of Technology            |

| Dr. ir.        | E. de Groote     | University of Twente (special expert)         |

| Prof. dr.      | J. N. Kok        | University of Twente (chairman and secretary) |

# UNIVERSITY OF TWENTE.

Faculty of Electrical Engineering, Mathematics and Computer Science, Computer Architecture for Embedded Systems (CAES) group

IDS Ph.D. Thesis Series No. 18-463 Institute on Digital Society PO Box 217, 7500 AE Enschede, The Netherlands

NWO Applied and Engineering Sciences

This work is part of the research program 'Integrated Design Approach for Safety-Critical Real-Time Automotive Systems' with project number 12698, which is financed by NXP and the Netherlands Organization for Scientific Research (NWO). Project leader : Prof. dr. ir. M.J.G. Bekooij

Copyright © 2019 Guus Kuiper, Enschede, The Netherlands. This work is licensed under the Creative Commons Attribution-NonCommercial 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc/ 4.0/deed.en\_US.

This thesis was typeset using LATEX, TikZ, and Kile. This thesis was printed by Gildeprint Drukkerijen, The Netherlands.

| ISBN | 978-90-365-4541-9                             |

|------|-----------------------------------------------|

| ISSN | 2589-4730; IDS Ph.D. Thesis Series No. 18-463 |

| DOI  | 10.3990/1.9789036545419                       |

### ACCURATE ANALYSIS OF REAL-TIME STREAM PROCESSING APPLICATIONS

USING DATAFLOW MODELS AND TIMED AUTOMATA

Proefschrift

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. T. T. M. Palstra, volgens besluit van het College voor Promoties in het openbaar te verdedigen op vrijdag 8 maart 2019 om 16.45 uur

door

Guus Kuiper

geboren op 29 januari 1988 te Doetinchem Dit proefschrift is goedgekeurd door:

Prof. dr. ir. M. J. G. Bekooij (promotor)

Copyright © 2019 Guus Kuiper ISBN 978-90-365-4541-9

# Abstract

Autonomous cars are an example of a safety-critical Cyber-Physical System (CPS). In such a CPS, there is a very complicated interaction between the continuoustime physical environment and the discrete-time embedded control system of the car using its sensors and actuators. The sensors periodically sample the physical properties of the environment and produce streams of data samples. The actuators consume data from streams and expect to receive this data periodically from the digital control system. In this thesis, we focus on the modem system in autonomous cars, which is used for vehicle-to-vehicle communication. Such a safety-critical embedded system must be analyzed in order to verify whether temporal constraints will be satisfied. During the design of such a system, bounds must therefore be derived for the interval of time it takes for a real-time system to produce an output as a response to an input event.

Nowadays, these embedded systems are often implemented on multiple processors. The software that is running on such a system is split into tasks, that are connected by First-In-First-Out (FIFO) communication buffers. Some of these tasks execute conditionally, depending on the value of the incoming data. The incoming data can put the application in a certain *mode*, in which only a subset of tasks actually executes. Run-time schedulers determine when a task is allowed to execute on a processor.

The available analysis methods for this type of systems have severe shortcomings. The analysis results of these methods are insufficiently accurate. Furthermore, the run-time of the analysis methods is often unacceptably high. Moreover, most of these methods do not support applications containing cyclic dependencies and dynamic applications containing conditionally executed tasks.

The analysis of applications containing cyclic dependencies naturally fits to dataflow analysis approaches. However, for dynamic applications where tasks are scheduled using budget schedulers, the accuracy of dataflow analysis can be low. We therefore introduce *locks* that cause additional sequence constraints in these dynamic applications. These locks prevent interference between tasks in different modes, which can reduce the latency for dynamic applications.

To enable the analysis for non-starvation-free schedulers, we also introduce *barriers*. These non-starvation-free schedulers are a broader class than budget schedulers. The barriers ensure that all inputs of a mode are available before any tasks in that mode can start. The combination of locks and barriers allows for compositional analysis of modes. This means that each mode can be analyzed in isolation, even if these modes belong to a different level in the hierarchy of an application. As a

result, existing analysis methods for non-dynamic applications can be used for each mode in isolation.

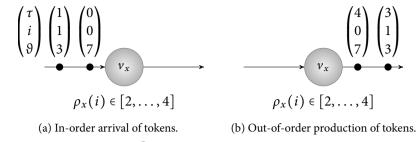

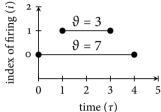

To obtain more accurate analysis results, we introduce a *transformation* from dataflow graphs into timed automata. Using these timed automata, accurate analysis can be performed by taking the correlation of firing durations into account of consecutive firings of the same task, but also of different tasks. Current dataflow analysis techniques abstract from this specific type of correlation by means of overapproximation, whereas we can take this correlation into account with timed automata, without over-approximation. Moreover, we enable the analysis of systems with out-of-order communication by annotating tokens with a token index order, instead of only using the token arrival order. Out-of-order communication can be a result of multiple executions of the same tasks in parallel. By consuming tokens in index order, the functional behavior of the graph is orthogonal to the arrival order of the tokens.

In order to accurately analyze the consequences of pre-emptive task scheduling on the temporal behavior of an application, we make use of model checking of timed automata. In this model we include correlation of the executions of different tasks, sharing the same resource. However, modeling task scheduling directly in a timed automata model can make the scheduling problem undecidable. We address this issue by either an over-approximation in the timed automata model, or by allowing the model checker to over-approximate reachability. The run-time of the analysis method is improved by combining model checking of timed automata with dataflow analysis. Moreover, latency is minimized by using this *hybrid analysis/optimization* method, where we introduce additional *sequence constraints* to limit the interference between tasks.

# SAMENVATTING

Autonome auto's zijn een voorbeeld van een veiligheidskritisch Cyber-Physical System (CPS). In zo een CPS is er een zeer gecompliceerde interactie tussen de continue tijd van de fysieke omgeving van het systeem en de discrete tijd van het embedded controlesysteem in een auto. Sensoren samplen de fysieke eigenschappen van de omgeving periodiek en produceren hier data stromen van. Actuatoren lezen data uit stromen, waarbij ze deze data periodiek verwachten te ontvangen van het digitale besturingssysteem. In dit proefschrift concentreren we ons op het modem systeem binnen autonome auto's, die wordt gebruikt voor voertuig-naarvoertuigcommunicatie. Een dergelijk veiligheidskritisch embedded systeem moet worden geanalyseerd om na te gaan of aan eisen wat betreft timing wordt voldaan. Tijdens het ontwerp van een dergelijk systeem moeten daarom grenzen worden afgeleid voor het tijdsinterval dat een real-time systeem nodig heeft om een reactie te produceren op een gebeurtenis.

Tegenwoordig worden deze embedded systemen vaak geïmplementeerd op meerdere processoren. De software die op een dergelijk systeem wordt uitgevoerd, is opgesplitst in taken die zijn verbonden door First-In-First-Out (FIFO) communicatiebuffers. Sommige van deze taken worden conditioneel uitgevoerd, afhankelijk van de waarde van de binnenkomende data. De inkomende gegevens kunnen de applicatie in een bepaalde *modus* plaatsen, waarin slechts een deel van de taken daadwerkelijk wordt uitgevoerd. *Run-time schedulers* bepalen wanneer een taak mag worden uitgevoerd op een processor. Helaas hebben de beschikbare analysemethoden voor dit soort systemen ernstige tekortkomingen.

Een van de problemen van de analysemethoden is dat de analyseresultaten voor dit type systemen zijn onvoldoende nauwkeurig. Bovendien is de rekentijd die de analysemethoden nodig hebben om tot een resultaat te komen vaak onaanvaardbaar hoog. Bovendien ondersteunen de meeste van deze methoden geen applicaties die cyclische afhankelijkheden bevatten en dynamische applicaties met conditioneel uitgevoerde taken.

De analyse van applicaties die cyclische afhankelijkheden bevatten, past van nature bij dataflow-analysetechnieken. Voor dynamische applicaties waarbij taken worden gepland met behulp van *budget schedulers*, kan de nauwkeurigheid van analyse echter laag zijn. Daarom introduceren we *locks* die extra beperkingen in de executievolgerde van taken toevoegen in deze dynamische applicaties. Deze *locks* voorkomen interferentie tussen taken in verschillende modi, wat de latentie voor dynamische applicaties kan verminderen.

Om de analyse voor non-starvation-free schedulers mogelijk te maken, introduceren

we ook *barriers*. Deze schedulers zijn een bredere klasse dan budget gebaseerde schedulers. De barriers zorgen ervoor dat alle inkomende data van een modus beschikbaar is voordat taken binnen die modus worden uitgevoerd. De combinatie van locks en barriers maakt compositieanalyse van modi mogelijk. Dit betekent dat elke modus afzonderlijk kan worden geanalyseerd, zelfs als deze modi tot een ander niveau in de hiërarchie van een applicatie behoren. Echter, kunnen bestaande analysemethoden voor niet-dynamische applicaties voor elke modus afzonderlijk worden gebruikt.

Voor meer accurate analyseresultaten introduceren we een transformatie van dataflow-grafen naar *timed automata*. Met behulp van deze timed automata kan een nauwkeurige analyse worden uitgevoerd door de correlatie van vuurtijden mee te nemen, zowel bij opeenvolgende vuringen van dezelfde taak, als tussen verschillende taken. Huidige dataflow-analysetechnieken abstraheren van deze correlatie door middel van over-approximatie, terwijl we deze correlatie mee kunnen nemen met timed automata, zonder over-approximatie. Bovendien maken we de analyse mogelijk van systemen met niet-sequentiele communicatie door tokens met een *token-indexvolgorde* te annoteren, in plaats van alleen de token-aankomstvolgorde te gebruiken. Niet-sequentiele communicatie kan het resultaat zijn van meerdere uitvoeringen van dezelfde taken in parallel. Door tokens in indexvolgorde te consumeren, is het functionele gedrag van de grafiek orthogonaal ten opzichte van de aankomstvolgorde van de tokens.

Om de consequenties van onderbreekbare taakplanning op het temporele gedrag van een applicatie nauwkeurig te analyseren, maken we gebruik van modelcontrole van timed automata. Het rechtstreeks modelleren van taakplanning in een timed automatamodel kan het planningsprobleem onbeslisbaar maken. We pakken dit probleem aan door een overschatting in het timed automatamodel, of door de modelcontrole een overschatting te laten maken. De looptijd van de analysemethode is verbeterd door modelcontrole van getimede automaten te combineren met dataflow-analyse. Bovendien wordt de latentie geminimaliseerd door gebruik te maken van deze hybride analysemethode, waarbij we extra volgordebeperkingen introduceren om de interferentie tussen taken te verminderen.

# Dankwoord

Eindelijk is het dan zo ver; mijn promotie komt in zicht, en de laatste hand wordt gelegd aan dit boekwerk. Vier jaar lang heb ik aan mijn onderzoek morgen werken, met als eindresultaat dit boekwerk. Deze periode was heel anders dan het jaar wat ik nu bijna al binnen het bedrijfsleven aan de slag ben. Nu werk ik bij Demcon/Bond met een groot multidiciplinair team samen aan een groot doel. Bij een promotie ga je toch meer voor eigen resultaten, uitgedrukt in de vorm van publicaties. Mijn promotie was dus meer werk op een eilandje. Echter had ik dit niet kunnen doen zonder hulp of steun. Vandaar dat ik de nodige mensen wil bedanken.

Als eerste Marco, mijn promotor. Lang geleden begon ik mijn afstudeeropdracht onder jouw supervisie. Niet in de analysetechnieken, maar hardware / chip design. Ook hier ging het al over het kunnen geven van garanties, de "rotonde met stoplichten", maar dan voor latency voor de communicatie binnen een chip. Hier heb je mij toch langzaam overtuigd van de analysewereld. Deze hemel waarin alle componenten zich ideaal gedragen. Terwijl er in de echte wereld onverwacht, vanalles mis kan gaan, en aannames die je maakt ineens niet meer op kunnen gaan. Jouw diepgaande technische kennis zorgde dat we elke discussie weer een stapje verder kwamen richting een paper. Daarnaast kan ik ook jouw uitgebreide feedback waarderen op het minst favoriete onderdeel van de promotie, het daadwerkelijk opschrijven van de onderzoeksresultaten. Dit is vooral knap gezien je maar part-time, één dag in de week, professor bent bij CAES naast je reguliere werk bij NXP. Wat voor type scheduler wordt er voor deze Marco resource gebuikt om je tijd zo te verdelen tussen de vele promovendie en afstudeerders? Parallellisatie zou dit scheduling probleem een stuk makkelijker, maar is in dit geval lastig te implementeren zolang het klonen van mensen nog niet echt een ding is.

Hiernaast zijn er meer mensen die zich inhoudelijk met mijn promotie bezig hebben gehouden. Philip, Joost, en Stefan waren de dataflow experts bij CAES die mij goed geholpen hebben met mijn papers, ook al zaten jullie ver weg in Einhoven bij NXP, wat de samenwerking er niet makkelijker op maakte. Als we dan wel een keer bij elkaar zaten bij de SCOPES conferentie, hadden jullie veel feedback op mijn conferentiepresentatie. Dit commentaar heb ik toen een paar uur voor mijn presentatie nog meer net allemaal kunnen verwerken voordat ik de echte presentatie mocht houden. Daarnaast was Robert met zijn dataflow expertise wel altijd in de buurt, en had hij altijd een interresant dataflow probleem om de tijd mee te vullen. Ook de afstudeerders; Oscar, Viktorio, Daniel, Mark en Oguz, mag ik niet vergeten. Al waren jullie onderzoeken niet direct relavant voor mijn promotie, jullie mogen begeleiden was wel een leuke afwisseling op mijn eigen onderzoek. Naast de inhoudelijk ondersteuning bracht mijn vakgroep, CAES, nog zoveel meer. Met Gerard aan het hoofd van de vakgroep was CAES een gezellige groep om deel van uit te maken, waar ik 5 jaar lang met veel plezier heb gezeten. Vooral de vrijdagmiddagborrels en koffiepauzes waren een goede manier om vernieuwde inspiratie op te doen. Vooral dankzij de inzet van Gerwin. De secretaresses, Marlous, Nicole en Thelma, ook bedankt voor de ondersteuning, vooral bij het regelen van de conferentiereizen. Ook Jochem verdient een bedankje voor de template voor dit boekje. Deze is verder ontwikkeld en beschikbaar gemaakt op Github voor de geïnteresseerden<sup>1</sup>.

Wat misschien nog wel het belangrijkste is aan een promotie, is alles er omheen. Je hoofd leeg maken, wat bij mij goed ging door te gaan sporten. Dankzij de vele Messed Uppers heb ik de problemen van de promotie aan de kant gezet bij trainingen, wedstrijden, toernooien en feestjes. Net als bij een promotie zijn hier zo de up en downs (hebben we dit seizoen al een wedstrijden gewonnen in de Eredivisie?). De vakantie en etentjes met de vrienden uit Doetinchem, EJ, Hans, Martin, Niels en Tjerk, zorgden voor de nodige afleiding. Wat is er beter dan inspiratie op doen met jullie op een strand in Bali, of tussen de vogels in een mangrovebos in Senegal? Ook de nieuwe collega's bij DEMCON/Bond zorgen voor een leuke werksfeer zodat het ook niet zo erg is om 's avond de laatste loodjes van mijn proefschrift kan afronden.

Als laatste wil ik mijn familie nog bedanken. Pap, en mam, ook al snappen jullie totaal niet waar ik me de afgelopen 4 jaar mee bezig heb gehouden, toch waren jullie altijd geïnteresseerd in mijn onbegrijpbare verhalen. Luc, jij stond altijd klaar bij Gringo's om mij aan de drank te helpen, als ik dat weer eens nodig had. Donna, jij hebt vast wat van je overvloedige energie aan mij overgedragen om mijn promotie af te kunnen ronden. Nienke, zonder jou was ik vast niet zo ver gekomen met mijn promotie, had ik een saaie foto op de cover gehad, zaten er nog veeeel meer spelfouten in dit boekje, ....

Guus Enschede, januari 2019

<sup>&</sup>lt;sup>1</sup>https://github.com/gkuiper/phdthesis-template

# Contents

| 1 | Int | RODUCTION                                                                                         | 1           |

|---|-----|---------------------------------------------------------------------------------------------------|-------------|

|   | 1.1 | Cyber-Physical Systems                                                                            | 2           |

|   | 1.2 | Real-time systems      1.2.1    Run-time scheduling      1.2.2    Analysis of run-time scheduling | 4<br>6<br>8 |

|   | 1.3 | Problem statement                                                                                 | 10          |

|   | -   | Contributions                                                                                     |             |

|   | 1.4 |                                                                                                   | 11          |

|   | 1.5 | Outline                                                                                           | 12          |

| 2 | BAG | CKGROUND                                                                                          | 15          |

|   | 2.1 | Model checking                                                                                    | 16          |

|   |     | 2.1.1 Transition systems                                                                          | 17          |

|   |     | 2.1.2 Reachability analysis                                                                       | 18          |

|   |     | 2.1.3 Bisimulation                                                                                | 19          |

|   |     | 2.1.4 Timed automata                                                                              | 21          |

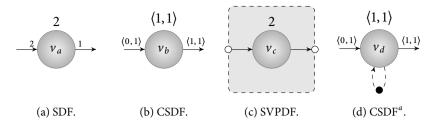

|   | 2.2 | Dataflow models                                                                                   | 25          |

|   |     | 2.2.1 Properties of dataflow models                                                               | 27          |

|   |     | 2.2.2 More expressive dataflow models                                                             | 28          |

|   |     | 2.2.3 Analysis                                                                                    | 30          |

|   | 2.3 | Analysis models for concurrent systems                                                            | 31          |

|   | 2.4 | Summary                                                                                           | 33          |

| 3 |     | FORCING MUTUALLY EXCLUSIVE TASK EXECUTION IN MODAL                                                | 35          |

|   | 3.1 | Related work                                                                                      | 37          |

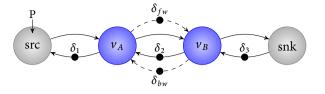

|   | 3.2 | Basic idea                                                                                        | 39          |

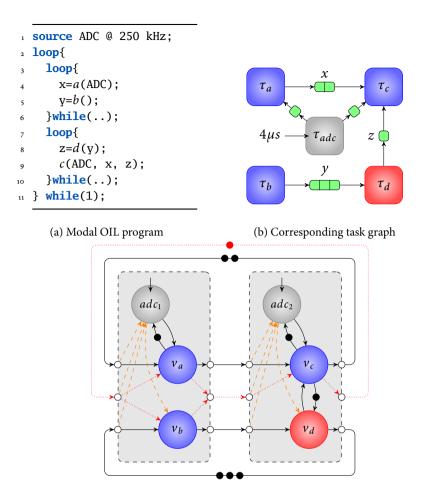

|   | 3.3 | Types of mutual exclusivity                                                                       | 43          |

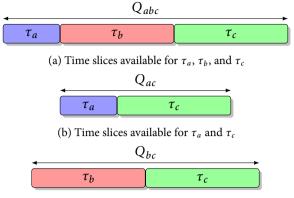

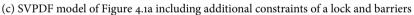

|   | 3.4 | Response times TDMA                                                                               | 44          |

|   | 3.5 | Real-time lock implementation                                                                     | 45          |

|   |     | 3.5.1 Realization                                                                                 | 45          |

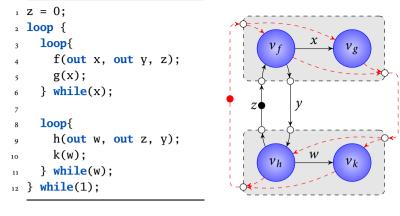

|   |     | 3.5.2 Code Generation                                                                             | 48          |

|     | 3.5.3    | Dea  | dlock | :-free | edor  | п.  | •    | • • | •   | • | • • | • | • | ٠ | ٠ | • | • | • | <br>• | ٠ | ٠ | • | • | • | • | 51 |

|-----|----------|------|-------|--------|-------|-----|------|-----|-----|---|-----|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|----|

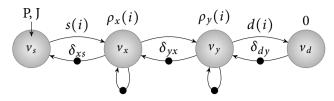

| 3.6 | SVPDF    | mo   | del . |        | • •   |     |      |     |     | • |     |   |   | • |   |   |   |   |       | • | • |   |   |   |   | 52 |

| 3.7 | Lock fro | om s | seque | entia  | al sj | pec | cifi | cat | ioi | 1 |     |   |   | • |   |   |   |   |       | • | • |   |   |   |   | 53 |

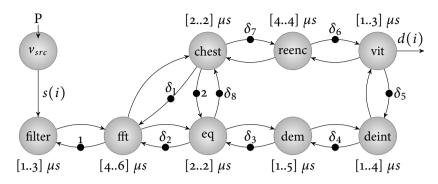

| 3.8 | Case stu | udy  |       |        | • •   |     |      |     |     | • |     |   |   | • |   |   |   |   |       | • | • |   |   |   |   | 55 |

| 3.9 | Conclus  | sion |       |        |       |     |      |     |     |   |     |   |   |   | • |   |   |   |       |   |   |   |   |   |   | 58 |

| Сог | mpositional analysis of modes and FPP scheduling                      | 61       |

|-----|-----------------------------------------------------------------------|----------|

| 4.1 | Related Work                                                          | 63       |

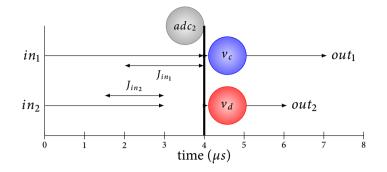

| 4.2 | Basic idea                                                            | 64       |

| 4.3 | Analysis flow         4.3.1       Flattening of a hierarchical level  | 67<br>69 |

| 4.4 | Periodic source constraints                                           | 72       |

| 4.5 | Response times      4.5.1      Mutual exclusive execution using locks | 73<br>74 |

| 4.6 | Response times larger than period                                     | 76       |

| 4.7 | Case study                                                            | 77       |

| 4.8 | Conclusion                                                            | 82       |

| 5 | LAT | ENCY ANALYSIS USING TIMED AUTOMATA                     | 85  |

|---|-----|--------------------------------------------------------|-----|

|   | 5.1 | Related work                                           | 87  |

|   | 5.2 | The HSDF <sup><i>a</i></sup> model                     | 87  |

|   | 5.3 | Max-plus Semantics of HSDF <sup>a</sup>                | 89  |

|   | 5.4 | Extended timed automata                                | 91  |

|   | 5.5 | Timed automata model of HSDF <sup>a</sup> graphs       | 92  |

|   |     | 5.5.1 Uppaal components                                | 92  |

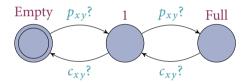

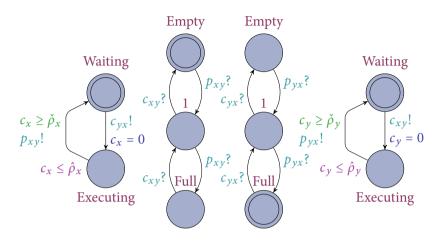

|   |     | 5.5.2 Dataflow edge model                              | 93  |

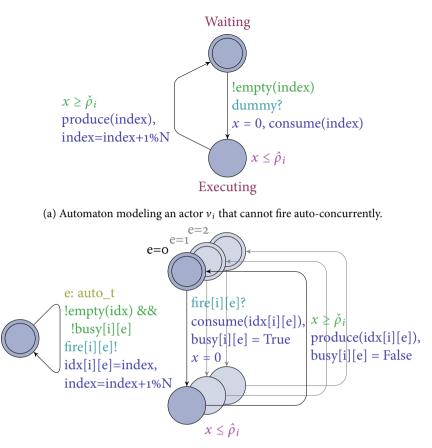

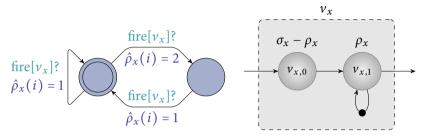

|   |     | 5.5.3 Actor model                                      | 95  |

|   |     | 5.5.4 Complete automaton of an HSDF <sup>a</sup> graph | 97  |

|   |     | 5.5.5 Integer clock constraints                        | 98  |

|   | 5.6 | Case study                                             | 98  |

|   | 5.7 | Conclusion                                             | 101 |

| 6   | Нун   | BRID LATENCY ANALYSIS                                                                              | 105                             |

|-----|-------|----------------------------------------------------------------------------------------------------|---------------------------------|

|     | 6.1   | Introduction                                                                                       | 105                             |

|     | 6.2   | Related work                                                                                       | 107                             |

|     | 6.3   | Basic idea                                                                                         | 109                             |

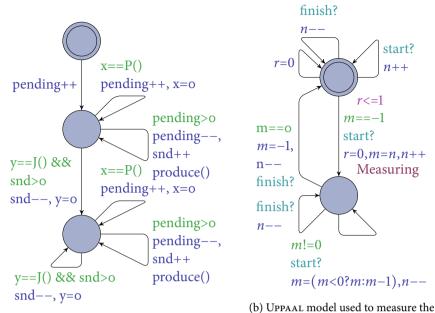

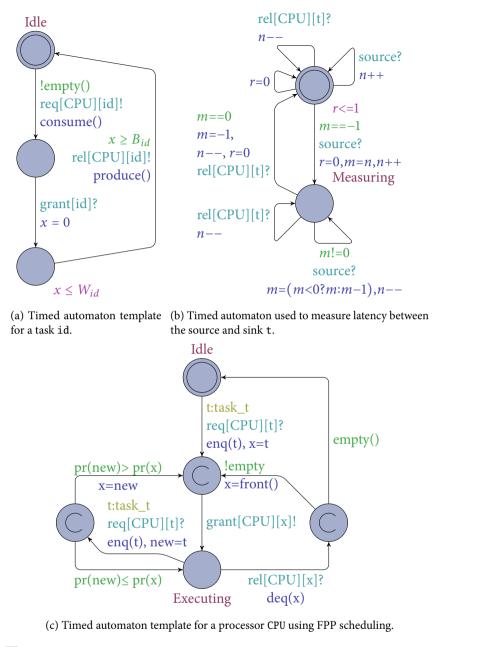

|     | 6.4   | Timed automata6.4.1FIFO buffer6.4.2Task template6.4.3Processor template6.4.4Verification           | 110<br>110<br>110<br>112<br>113 |

|     | 6.5   | Timed-dataflow6.5.1Deadlock6.5.2Minimum guaranteed throughput6.5.3Approximative dataflow analysis  | 113<br>113<br>114<br>114        |

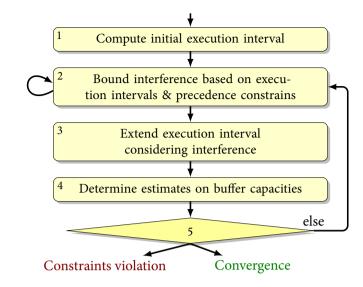

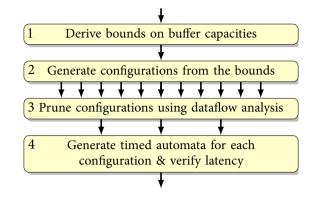

|     | 6.6   | Hybrid analysis                                                                                    | 115                             |

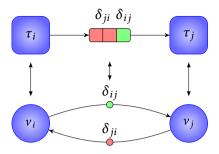

|     | 6.7   | Sequence constraints         6.7.1       Negative tokens         6.7.2       Redundant constraints | 116<br>119<br>119               |

|     | 6.8   | Case study                                                                                         | 121                             |

|     | 6.9   | Conclusion                                                                                         | 125                             |

| 7   | Cor   | ICLUSION                                                                                           | 127                             |

|     | 7.1   | Summary                                                                                            | 128                             |

|     | 7.2   | Contributions                                                                                      | 129                             |

|     | 7.3   | Recommendations for future work                                                                    | 131                             |

| Ac  | RONY  | MS                                                                                                 | 135                             |

| S¥I | MBOL  | s                                                                                                  | 137                             |

| B11 | BLIOG | RАРНY                                                                                              | 139                             |

| Lis | T OF  | Publications                                                                                       | 147                             |

| Ini | DEX   |                                                                                                    | 149                             |

xiii

CONTENTS

xiv

# INTRODUCTION

Cars have had no radical changes to their design for decades, until recently. Fossil fuels are running out quickly, which leads to the need to use renewable energy sources. As a result, electrical cars have started to emerge. The next major innovation in the automotive industry will likely be autonomous driving.

The trend to increase the level of autonomy of cars imposes great challenges to their design. There is a very complicated interaction between the physical environment, sensors observing the environment, the hardware and software processing these observations and taking actions, and the actuators of the car. The interaction between these components, in for example autonomous cars, results in a system that is known as a Cyber-Physical System (CPS).

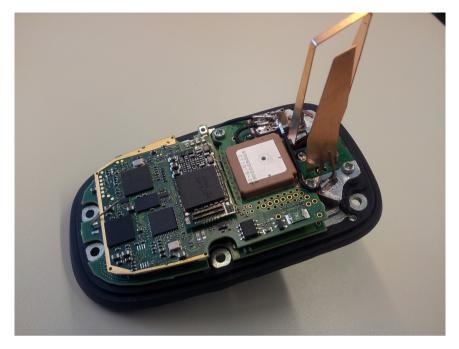

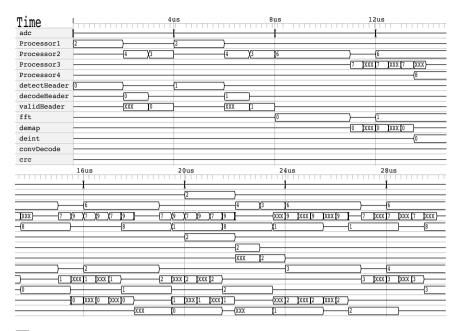

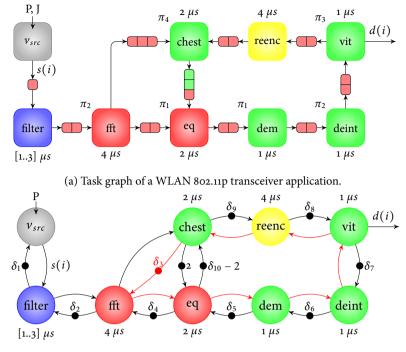

An increasing amount of data is processed by cars in order to provide a certain level of autonomy. Sensors in cars produce this data by observing the environment. However, more intelligent autonomous cars also take advantage of communication with nearby vehicles. These cars are equipped with vehicle-to-vehicle communication systems, like the one shown in Figure 1.1. In this thesis we will focus on the modem subsystem of these vehicle-to-vehicle communication systems.

There are very strict demands on the temporal behavior of the modem system in autonomous cars, since these cars are safety-critical systems. Incorrect or too late decisions can have disastrous consequences. Using the vehicle-to-vehicle communication system, a car must respond quickly to a sudden braking action of a closely preceding car, to prevent collisions. During the design of such a modem subsystem, we want to provide guarantees about the worst-case temporal behavior of that subsystem. In this thesis we will therefore describe new models and analysis techniques that can be used to provide such temporal guarantees.

The modem application is computationally intensive, since it has to deal with rapidly changing channel conditions. Therefore, the modem is usually implemented on a

Figure 1.1: A shark fin shaped modem system of WISI Automotive for vehicle-to-vehicle communication (Photo by Business Wire).

multiprocessor system. In this thesis we will analyze applications that are implemented on such multiprocessor systems.

The outline of this chapter is a follows. CPSs are described in more detail in Section 1.1. We then expand upon the digital processing part of these CPSs that must satisfy temporal constraints in Section 1.2. There, we also compare existing analysis approaches for these type of systems and their shortcomings. The main problem addressed in this thesis is formulated in Section 1.3. The contributions of this thesis towards improving the analysis methods are summarized in Section 1.4. Finally, the outline of this thesis is presented in Section 1.5.

#### 1.1 CYBER-PHYSICAL SYSTEMS

The applications we are targeting in this thesis receive their incoming data from the environment, process it, and transmit the corresponding output back to the environment. The data is often processed on an *embedded system*, which is a computer system designed for a specific application. The interaction between the physical environment and the computational part in the form of an embedded system forms a CPS.

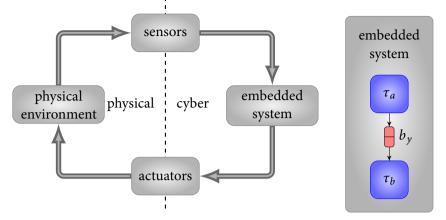

(a) The components that construct a Cyber-Physical System: physical environment, sensors, embedded system and actuators.

(b) The embedded system within a CPS

Figure 1.2: An overview of the components of a Cyber-Physical System (CPS) (a) and the embedded system inside a CPS (b).

A Cyber-Physical System is defined as:

A computing system that is tightly coupled with its physical environment, where algorithms running on the computing system interact with the physical environment, based on the inputs received from sensors measuring properties of the physical environment.

Such a CPS encompasses both the *continuous-time* domain of the physical environment, and a *discrete-time* domain in the embedded system. On the boundaries of these two domains, a conversion is made from continuous-time signals to discrete-time signals and vice versa. A *sensor* performs the task of converting a continuous time signal to a discrete signal. The continuous-time signals are sampled by a sensor *periodically*: a sample is taken from the continuous-time signal and transforms it into a continues-time signal. Hence, sensors and actuators perform the opposite conversion. Figure 1.2a shows how these components together form a CPS.

In this thesis we focus especially on modem applications for vehicle-to-vehicle communication. The wireless communication channel is the physical environment in this type of CPSs. The modem consists of both a receiver and transmitter, where the receiver decodes samples produced by an Analog-to-Digital Converter (ADC) and the transmitter encodes samples, which are sent to a Digital-to-Analog Converter (DAC).

We consider embedded systems that execute *stream processing applications*. This are applications that process endless streams of samples. Internally, a stream processing application can be subdivided into *tasks*, as shown in Figure 1.2b. Each task

performs a part of the stream processing application. The output of a task, which thus forms an intermediate result of the application, is typically communicated to other tasks using First-In-First-Out (FIFO) *buffers*. One task writes data into the buffer, whereas another task reads data from it. In case there is insufficient data in the buffer, the task that reads is blocked; i.e. it has to wait until data arrives before it can continue to execute. Moreover, these FIFO buffers have a finite size, such that a task that wants to write data into a buffer is blocked in case the buffer is already full. These finite-sized buffers therefore create cyclic dependencies in applications. The advantage of using FIFO buffers is that they allow for functionally deterministic exchange of data.

The applications we consider are either *static* or *dynamic*. In the static case, the rate at which tasks in the application execute is determined by the sample rate of the sensors. However, in the dynamic case, tasks can be *executed conditionally*. Tasks are said to execute conditionally if the values of the incoming data determine whether the tasks will actually execute or not. A task that does not execute, also does not produce data into its output buffers. The behavior of dynamic applications can therefore change depending on the physical environment. These dynamic applications are also called *modal applications*, because the execution of tasks can depend on previously received data, which puts the application in a particular *mode*. In this thesis we will consider both modal applications and static applications.

Although the use of FIFO buffers in applications itself can result in functionally deterministic behavior, this does not hold for the buffers at the boundaries of the application. Buffers that are filled by sensors, or read by actuators behave differently. These sensors and actuators execute time-triggered, instead of tasks that execute data-driven. These two execution schemes, time-triggered and data-driven execution, are discussed in more detail in the next section. If the throughput constraint that is imposed by these sensors and actuators is not fulfilled, buffer overflows or underflows can occur. A buffer overflow results in loss of samples. In case of a buffer underflow, the last sample is repeated. These buffer overflows and underflows lead to undesirable functionally non-deterministic, and thus unpredictable, behavior. The embedded system is therefore subjected to throughput constraints, which makes this system a real-time system. Real-time systems are discussed in more detail in the next section.

#### 1.2 REAL-TIME SYSTEMS

The type of embedded systems we address in this thesis must satisfy strict temporal constraints. These systems are therefore real-time systems.

#### A real-time system is defined as:

A system of which the correctness of their results not only depends on the values as an outcome of a computation, but also on the moment in time at which these values are produced.

In such a real-time system, tasks are characterized by the time it takes to perform one execution, which is called the *execution time* of a task. An execution of a task may start when there is sufficient data for a task to read from all its input buffers. After a task finishes its execution, data is written to its output buffers. The execution time of a task is typically not a constant. Therefore, an upper bound on the execution time is specified. This upper bound is called the Worst-Case Execution Time (WCET). The Best-Case Execution Time (BCET) is a lower bound on the execution time of a task.

In this thesis we consider embedded systems with multiple processors such that sufficient computational performance is available to meet temporal requirements. Tasks can either execute on different processors in *parallel*, or some tasks can execute interleaved in time on the same processor *concurrently*. A *scheduler* determines the moment in time at which a task is executed on a processor. We consider systems where tasks are scheduled on a per-processor-basis, therefore there is a scheduler for each processor. The assignment of tasks to processor system.

Two task scheduling policies exist: time-triggered and data-driven. In time-triggered scheduling policies, the start of an execution of a task is performed based on a timer. For data-driven schedulers, scheduling is performed based on the arrival of data. In the latter case, the application is less sensitive to variations in the execution times. A sporadic longer execution of a task can in some cases be compensated by shorter consecutive executions to still meet the temporal constraints on the execution of the application. Such an aperiodic, data-driven, scheduling policy can exploit a tighter workload characterization of tasks than the WCET characterization [Hau15]. In this thesis we develop techniques that exploit these tighter workload characterizations.

Many real-time applications contain *cyclic dependencies*. These cyclic dependencies can be a result of feedback loops and the use of bounded FIFO buffers for inter-task communication. These cyclic dependencies can bound the number of concurrent executions of tasks on the cycle. Although these cyclic dependencies can result in better analysis results, they complicate the analysis of real-time systems.

Analysis of a real-time system is required in order to verify whether the system satisfies its temporal constraints. Therefore, we need to analyze systems with the combination of tasks with: cyclic dependencies, variable execution times, parallel execution of tasks, and the effect of run-time scheduling. A temporal constraint of the system can be in the form of a maximum *latency*. The *latency* is the time difference between the time at which a sample was produced by a sensor and the corresponding sample was consumed by an actuator.

Sensors often produce samples periodically, and therefore impose a *throughput* constraint on the real-time system. This means that the throughput of each individual task, as well as the combined throughput of all communicating tasks, should be verified for satisfying the throughput constraint. Analysis models for real-time

Figure 1.3: Classes of run-time schedulers.

systems that can express the combination of tasks with cyclic dependencies, variable execution times, and that include the effect of scheduling, are discussed in Chapter 2. In that chapter, we also address the analysis of these models.

#### 1.2.1 RUN-TIME SCHEDULING

A *scheduler* performs arbitration for a *shared resource*, a processor in this case, using a certain scheduling policy. In this section, we introduce three classes of schedulers for real-time systems. After this introduction, we compare existing analysis approaches for these systems and the techniques behind these approaches in Subsection 1.2.2.

A task that is ready to start its execution on a processor can be delayed by the scheduler if other tasks also want to execute on the same processor. This delay caused by other tasks is called *interference*. The *response time* of a task is the time between the moment a task is ready to start an execution and the finish time of that execution. The response time thus consists of both the execution time of the task and the interference caused by other tasks.

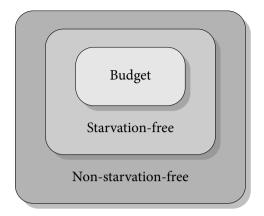

In [WBS09], three classes of run-time schedulers for real-time systems are defined:

- 1. Budget schedulers

- 2. Starvation-free schedulers

- 3. Non-starvation-free schedulers

The relation between these three classes of schedulers is illustrated in Figure 1.3. Budget schedulers are the least general class of schedulers, whereas non-starvationfree schedulers are the most general class in Figure 1.3.

These classes of schedulers can be distinguished based on the amount of knowledge that is required about the tasks that are being scheduled, in order to bound the

interference between tasks. The three classes can be distinguished based on two properties:

- 1. Execution times of all tasks sharing the same resource

- 2. Rate of execution of all tasks sharing the same resource

The execution time of a task is the time the task needs exclusive access to the processor to finish an execution. The execution rate of a task is the number of executions of a task during a certain time window.

Budget schedulers are the most restrictive class of schedulers we consider. The advantage of schedulers in this class is that no knowledge about execution times and execution rates of other tasks is required to provide a bound on the interference between tasks. An example of a budget scheduler is the Time Division Multiple Access (TDMA) scheduler. A budget scheduler assigns a minimum time budget to each task within a maximum time interval, the *replenishment interval*. During each interval, every task can execute for the duration of their assigned time budget. The sum of the budgets of all tasks logically adds up to the entire replenishment interval. The maximum interference a task can experience can therefore be derived independently for every task, i.e. without knowledge of the execution time and execution rate of other tasks.

The starvation-free schedulers belong to a larger class of schedulers. For these schedulers, only knowledge about the execution time of other tasks is required to upper bound the interference. The Round-Robin (RR) scheduler is the best known scheduler of this class. For a RR scheduler, all tasks may execute once, in a predefined order, until they are finished, after which this sequence repeats. For this reason, all other tasks can execute at most once, before the task under consideration is executed. Therefore, knowledge of only the execution times is sufficient to determine the maximum interference.

The broadest class of schedulers is the class of non-starvation-free schedulers. Both the execution time and execution rate of other tasks are required to determine the interference between tasks. A well known scheduler inside this class is the Fixed Priority Pre-emptive (FPP) scheduler, which arbitrates tasks based on their priority. A task with a higher priority that becomes ready to execute, pre-empts a lower priority task, to quickly get access to the processor. The task with the higher priority causes interference on the lower priority tasks that are thereby delayed. Without knowledge about both the execution time and execution rate of all tasks with a higher priority, the worst-case situation is that a low priority task must wait indefinitely before its execution can start.

Out of these three classes of schedulers, systems with budget schedulers and starvation-free schedulers are relatively easy to analyze. However, in practice many real-time systems make use of non-starvation-free schedulers, although the use of these schedulers draatically complicates system analysis. System designers are often unaware of the consequence on the analysis of using non-starvation-free schedulers. In this thesis we focus on non-starvation-free schedulers.

| Analysis n     | nethod                | Multin | Code Stor | Crain den den den den den den den den den de | Buffer dependencies | Dinger acies | Run tin | ACUP 10 15 |

|----------------|-----------------------|--------|-----------|----------------------------------------------|---------------------|--------------|---------|------------|

| MAST           | [HGGM01]              | +      | +         | -                                            | -                   | -            | +       | _          |

| SymTA/S        | [HHJ <sup>+</sup> 05] | +      | +         | -                                            | -                   | -            | +       | -          |

| MPA-RTC        | [TS09]                | +      | +         | -                                            | -                   | -            | +       | -          |

| MPA-RTC        | [JPTY08]              | +      | -         | +                                            | -                   | -            | +       | -          |

| Dataflow       | [KHB16a]              | +      | +         | +                                            | +                   | -            | ++      | +-         |

| Timed automata | [HV06]                | +      | +         | -                                            | -                   | -            |         | +          |

| TIMES          | [AFM <sup>+</sup> 03] | -      | +         | +                                            | -                   | -            |         | +          |

| Our approach   | this thesis           | +      | +         | +                                            | +                   | +-           | -       | ++         |

Table 1.1: Comparison of analysis methods for systems with non-starvation-free schedulers.

#### 1.2.2 ANALYSIS OF RUN-TIME SCHEDULING

There are two main categories of analysis techniques for systems with non-starvation-free schedulers. The first computes a fix-point, and the second uses model checking, which is based on reachability analysis. In this section, we briefly introduce both categories of analysis techniques, and give a comparison of analysis approaches that utilize these techniques.

Many analysis approaches have been developed for the analysis of systems with non-starvation-free schedulers. Table 1.1 presents a number of these approaches and highlights system features that are supported (+) or not supported (-). The table also presents a rough estimate of their run-time and accuracy within the range of 'very good' (++) to 'very bad' (--). The run-time and accuracy of these approaches is heavily dependent on the system being analyzed, as is shown using a benchmarks for a number of approaches in [PWT<sup>+</sup>07].

Most of the fixed-point based analysis approaches are not able to analyze arbitrary task graphs. Especially cyclic data dependencies are problematic for MAST [HGGM01], SymTA/S [HHJ<sup>+</sup>05], and MPA-RTC [TS09]. MPA-RTC has been extended to support either cyclic data dependencies [TS09], or cyclic resource dependencies [JPTY08], but the combination of both is not yet supported.

Dataflow based analysis is suitable to analyze graphs that contain cyclic dependencies [Daso4, SB09]. These dependencies can even be exploited to obtain tighter analysis results using buffer sizing techniques [WGHB15]. Schedulers cannot be modeled directly in dataflow models unless the schedule is static [DSB<sup>+</sup>13]. However, the

effect of scheduling can be included in dataflow models. This was first shown for the class of budget schedulers [WBS09, LMC12]. Recently, the class of supported schedulers has been extended with non-starvation-free schedulers [HWGB13, HGWB14, LMB<sup>+</sup>14]. The dataflow analysis approaches also compute fixed-points. We focus on dataflow analysis in this thesis, since it supports the most system features as shown in Table 1.1. Moreover, cyclic data dependencies analysis and buffer sizing techniques have been developed that improve the accuracy of the analysis results.

Timed automata based approaches [HVo6, AFM<sup>+</sup>o<sub>3</sub>] are based on model checking, which uses reachability analysis. TIMES [AFM<sup>+</sup>o<sub>3</sub>] is an analysis tool that internally uses timed automata for the analysis of systems with non-starvation-free schedulers. However, it currently does not support systems with multiple processors. These timed automata based approaches produce accurate analysis results, but in general suffer from a large state space and therefore their run-time can be impractically large.

Before we state the differences between the two categories of analysis approaches, we need to explain fixed-point based analysis in more detail. A *fixed-point* is a value x of a function f for which f(x) = x. Loosely speaking, the least fixed-point of a function is the smallest value x for function f that is a fixed-point. Kleene's fixed-point theorem states that the unique least fixed-point of a Scott-continuous function can be computed by iteratively calling the function, starting at the least possible value. A function is Scott-continuous iff it preserves directed suprema. A Scott-continuous function is by definition also a *monotonic* function.

Functions can either be monotonic or non-monotonic. A function f is *monotonic* iff it is either entirely non-increasing, or entirely non-decreasing. As a results, there are two possible types of monotonic functions: for monotonically increasing functions, we have that  $\forall_{i \ge j}$ :  $f(i) \ge f(j)$ , and for monotonically decreasing functions, we have that  $\forall_{i \ge j}$ :  $f(i) \le f(j)$ . A function that does not satisfy any of these two conditions is non-monotonic. However, an approximation of such a non-monotonic function.

For the analysis of systems that include schedulers, we are interested in the fixedpoint of the function that calculates the interference a task can experience. Given a monotonic function for the maximum interference, the maximum interference is obtained by iterating the function starting with zero interference [TBW94]. This iterative computation of a fixed-point is often relatively fast. However, in general, the interference function is non-monotonic, and a monotonic over-approximation of the function needs to be constructed, before a fixed-point can be calculated.

Fixed-point based analysis approaches rely on abstracting from scheduling in order to create a monotonic model. Also non-determinism in an application, for example in the execution times of tasks, can be hidden using abstractions. This creates a *bounding abstraction* where only a worst-case and best-case bound of the system are analyzed [KB17]. These two bounds must include all possible behaviors of the system, since a monotonic over-approximation of the system is analyzed. As a results of these bounding abstractions, the analysis is computationally efficient. However, this efficiency of the analysis approaches based on the computation of fixed-points, comes with a potential loss of accuracy.

On the other hand, timed automata [AD94] do allow analysis of non-monotonic behavior and the expression of non-determinism. As a result, non-starvation-free schedulers can be modeled in timed automata. More accurate analysis can therefore be performed by model checking of these timed automata. The exact analysis of systems with the combination of pre-emptive schedulers, dependencies between tasks and non-constant execution times, as described in more detail in Chapter 6, is an undecidable analysis problem. Therefore, timed automata based analysis approaches also need to perform approximations to prevent undecidability. Since the analysis is performed on a system with non-monotonic components, it is insufficient to only analyze the worst-case and best-case behavior of each component. Therefore, all behaviors of the system must be included in the inclusion abstraction of the system [KB17]. This can lead to a traversal of a very large state space. While model checking of timed automata can lead to more accurate analysis results than analysis approaches based on the iterative computation of a fixed-point, the large state space causes it to be computationally intensive.

The comparison presented in this section shows that the holy grail of analysis approaches, for systems with non-starvation-free schedulers, does not exist. Current analysis approaches are not able to accurately analyze applications that contain arbitrary cyclic dependencies. Moreover, dynamic applications are also not considered by these approaches. Both fixed-point based approaches as well as reachability analysis using model checking have their advantages and disadvantages. A purely timed automata based analysis approach can analyze systems with non-monotonic behavior and non-determinism with a high accuracy, at the cost of a long run-time. The abstractions required to efficiently compute fixed-points iteratively, lead to a low accuracy of the fixed-point based approaches. This low accuracy, however, can be improved by exploiting cyclic data dependencies using dataflow analysis techniques. In this thesis we address these issues by combining dataflow bases analysis with model checking of timed automata.

#### **1.3 PROBLEM STATEMENT**

So far, we have introduced the type of systems that we address in this thesis: CPSs, of which we are interested in the real-time embedded system part. The implementation of the real-time system is targeted towards multiprocessor systems, where tasks are scheduled at run-time. Many analysis approaches exist for this type of systems, however, each approach has its downsides such as the restriction on the class of supported system features, a low accuracy or a very high run-time.

Therefore, the research problem that is addressed in this thesis is to:

Define techniques that improve the accuracy of the real-time analysis results, and also increase the class of real-time multiprocessor systems and applica-

tions that can be analyzed, while minimizing the run-time of the analysis algorithms.

Besides improvements of the analysis techniques, we also consider improvements to applications by adding locks and barriers that introduce so called *sequence constraints*. These sequence constraints limit the possible orders in which tasks can execute. As a result of these sequence constraints, the analysis can be simplified and the throughput, latency and accuracy can be improved.

This thesis describes dataflow analysis techniques for dynamic applications executed on multiprocessor systems with non-starvation-free schedulers. Furthermore, we show that a subclass of dataflow models can be modeled as timed automata. From the analysis results, it can be concluded that by applying model checking techniques, more accurate results can be obtained at the cost of a longer run-time. However, it also became apparent that it is impossible to guarantee exactness of the results for the considered analysis problem. Moreover, we will present an analysis technique that combines dataflow analysis and model checking that reduces the run-time without sacrificing accuracy. The work described in this thesis will also help to better understand the relation, similarities, and differences between model checking and dataflow based temporal analysis approaches.

#### 1.4 Contributions

The contributions presented in this thesis are:

- » Techniques to improve the throughput of modal applications on multiprocessor systems with budget scheduler by introducing a lock.

- » Techniques to enable the analysis of dynamic applications on multiprocessor systems with non-starvation free schedulers, by introducing a barrier.

- » Techniques to improve the analysis accuracy of static applications on systems without run-time schedulers by introducing a transformation of dataflow into timed-automata model.

- » Techniques to improve the analysis accuracy of static applications on systems with run-time schedulers by introducing a model of the run-time scheduler in timed automata. To achieve this, we encountered the issue that over-approximation must be applied to create a timed automata model. We observed long run-times especially when model checking methods were applied for buffer sizing.

- » Techniques to reduce the run-time of buffer sizing using model checking by proposing a combination of model checking with dataflow analysis to prune the search space.

- » Techniques to reduce the latency by proposing techniques to insert additional sequence constraints.

Summarizing; in this thesis we introduce real-time analysis techniques for static as well as dynamic applications. The analysis makes use of dataflow models and timed automata, and combines them to reduce the run-time of the analysis algorithms. Furthermore, additional sequence constraints are derived that improve the analysis results.

#### 1.5 OUTLINE

The analysis models used in this thesis, dataflow and timed automata, are introduced in Chapter 2, together with our view on the relation between these models. Chapter 3 introduces a *lock* to allow efficient analysis and resource usage when budget schedulers are used. Chapter 4 extends the analysis to the more general class of non-starvation-free schedulers by introducing *barriers*. The combination of locks and barriers allows hierarchical modes to be analyzed in isolation.

The subsequent part of this thesis addresses temporal analysis where we only consider a single mode. In Chapter 5, we improve the accuracy of the analysis of applications modeled as dataflow graphs by transforming the graphs into timed automata, which are model checked. Chapter 6 introduces a *hybrid analysis* flow, which combines computationally efficient dataflow analysis with model checking of timed automata. Additional *sequence constraints* are introduced in applications in order to reduce the latency.

Finally, Chapter 7 presents the conclusions of this thesis and gives recommendations for future work.

# BACKGROUND

Concurrent real-time applications running on multiprocessor systems are difficult to analyze. In 1965, Dijkstra identified one reason which is mutual exclusion [Dij65]. A classical example which illustrates issues caused by mutual exclusion, also by Dijkstra, is the dining philosophers problem. All philosophers sitting around a table should be able to alternate infinitly between thinking and eating, while sharing resources.

In order to analyze this interleaving of concurrent processes that together form an entire system, the system could be modeled in an analysis model. Analysis on such a model is used to analyze functional behavior such as deadlock, starvation and determinism. Next to the functional correctness, temporal behavior is crucial for real-time systems, and should also be verified using these analysis models.

Since we are interested in functionally correct systems, we restrict the systems we want to model to concurrent processes that communicate using FIFO buffers [Dij72]. This is opposed to systems that communicate using shared memory and requiring sort of locking, to guarantee mutual exclusive access to data structures, which prevents race conditions. Processes do not have any side-effects, except the interaction with buffers, and can only update their own state.

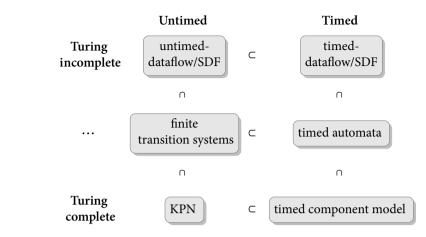

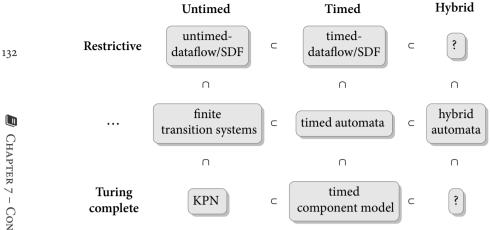

Throughout this thesis we use two timed analysis models: dataflow models and timed automata. The expressiveness of dataflow models is restricted, however, dataflow models can be analyzed efficiently. On the other hand, timed automata are very expressive, and many properties can be derived from them using model-checking. Since model-checking is based on state space exploration, and the state space is often large, the analysis of timed automata is less efficient and costs a large run-time.

In dataflow models, concurrent processes are specified as actors. Dependencies between these processes are represented by edges connecting actors. Together, these actors and edges form a directed graph. Cyclic dependencies in such a graph can

be used to bound the number of concurrent executions of actors on the cycle.

Each timed automaton executes sequential, however, multiple timed automata can execute concurrently. These timed automata communicate using so called hand-shaking actions. Communicating timed automata execute in parallel. A supervising scheduler can be modeled using timed automata, which grants access to a shared resource in a concurrent multiprocessor real-time system.

The two analysis models used in this thesis are discussed in more detail in this chapter: model checking of timed automata in Section 2.1 and dataflow models in Section 2.2. We use dataflow models throughout this entire thesis, whereas model checking of timed automata is relevant for Chapter 5 and Chapter 6. Furthermore, in Section 2.3 we compare the expressiveness of these two analysis models and place them in perspective to other related models.

#### 2.1 MODEL CHECKING

Formal verification of safety-critical systems using *model checking* [CE81] is becoming increasingly popular. The verification process using model checking is fully automated by tools like UPPAAL [DILS09], in contrast to providing proofs manually. Model checking usually requires the following steps: creation of a model of a system, simulation of the model, and finally formal verification of this model. A convenient representation of the model is in the form of graphs, as is the case for timed automata. Simulations of such a model can be used to compare the behavior of the model with the behavior of the system. If these differ, a revision of the model is required. The formal verification using the model consists of analyzing the state space of the model for certain properties specified in a temporal logic like Computation Tree Logic (CTL) [CE81]. When a property does not hold, a counterexample can be returned by the model checker [CGMZ95].

To understand model checking for real-time systems, we first consider the mathematical basis for model checking: transition systems. Then we discuss how to analyze these transition systems using reachability analysis. However, reachability analysis is not guaranteed to terminate for transition systems that include continuous time. Bisimulation is an equivalence relation between two transition systems; it can be used to prove that an abstraction with a finite state space exists of a system with an infinite size. The finite state space is the result of partitioning the continuous time of the state space into a finite number of regions, which together form a regions graph. Finally, timed automata are introduced based on these concepts. For timed automata a finite region graph can always be constructed, such that reachability analysis is guaranteed to terminate. We use timed automata later on in this thesis to analyze concurrent real-time multiprocessor systems.

#### 2.1.1 TRANSITION SYSTEMS

Computations of discrete systems can often be described as states with transitions between them. Such a *transition system* can formally be described as a directed graph,  $T = (S, Act, \rightarrow, S_0)$  where:

- » S is a set of states

- » Act is a set of actions

- »  $\rightarrow \subseteq S \times Act \times S$  is a transition relation

- »  $S_0 \subseteq S$  is a set of initial states

In the directed graph, the nodes are represented by the states and the edges are the transitions between different states.

A transition system starts in one of its initial states  $s \in S_0$ . In case there are multiple initial states, an initial state is selected non-deterministically from  $S_0$ . From there, the state of the system evolves to subsequent states according to the possible transitions  $\rightarrow$  in the system. A current state *s* transitions to a next state *s'* following the transition  $s \xrightarrow{\alpha} s'$ . During the transition the action  $\alpha \in Act$  is performed. Again, when there are multiple transitions possible from *s*, one of them is selected nondeterministically. This nondeterminism is crucial to describe concurrent systems [BKL08].

The set *S* and *Act* of a transition system is not required to be finite. However, for the transition system *T* to be finite, the size of *S* and *Act* must be finite.

For a transition system we can define the *direct successors* and *predecessors* of a state  $s \in S$  as Post(s) and Pre(s).

$$Post(s,\alpha) = \left\{ s' \in S \mid s \xrightarrow{\alpha} s' \right\}$$

(2.1)

$$Post(s) = \bigcup_{\alpha \in Act} Post(s, \alpha)$$

(2.2)

$$Pre(s, \alpha) = \left\{ s' \in S \mid s' \xrightarrow{\alpha} s \right\}$$

(2.3)

$$Pre(s) = \bigcup_{\alpha \in Act} Pre(s, \alpha)$$

(2.4)

This can be extended to sets of states  $C \subseteq S$ .

$$Post(C) = \bigcup_{s \in C} Post(s)$$

(2.5)

$$Pre(C) = \bigcup_{s \in C} Pre(s)$$

(2.6)

Using these definitions, a *terminal state* is defined as  $Post(s) = \emptyset$ . The set of terminal state  $S_f$  it holds that  $Post(S_f) = \emptyset$ . A transition system is deterministic if it holds  $\forall s, \alpha : |Post(s, \alpha)| \le 1$  and  $|S_f| \le 1$ .

#### Algorithm 1: Forward reachability

Input:  $S, S_0, S_f$ Initialization:  $W_0 = S_0, i = 0;$ repeat if  $W_i \cap S_f \neq \emptyset$  then  $| \_ return S_f$  reachable  $W_{i+1} = Post(W_i) \cup W_i;$ i = i + 1;until  $W_i = W_{i-1};$ return  $S_f$  not reachable

#### 2.1.2 REACHABILITY ANALYSIS

Properties of a transition system can be verified by *reachability analysis*. An error condition of a system can be encoded as a certain state in a transition system. Analysis on the transition system is used to conclude whether that state is reachable, and thereby conclude that the error can occur in the system. More sophisticated system properties may be specified in logic such as CTL, however, this is outside the scope of this thesis, but is explained in [BKL08]. We now focus on two simple reachability algorithms.

We discuss two reachability analysis algorithms that can be used to determine if a terminal state in  $S_f$  can be reached. One is the forward reachability algorithm whereas the other is the backward reachability algorithm. Both algorithms guarantee termination given finite transition systems. These reachability algorithms are modifications of standard graph traversal algorithms like Breadth-First Search (BFS) or Depth-First Search (DFS). These algorithms can further be extended to return a counter-example, showing the path to the terminal state in case it is reachable.

The *forward reachability* algorithm, see Algorithm 1, starts with the set of initial states  $S_0$  which is copied in the set  $W_0$ . This set is gradually extended during each iteration *i* of the algorithm with the successor states of that current set and stored in  $W_i$  using  $Post(W_i)$ , as defined in Equation 2.5. The algorithm terminates when no more states are added to  $W_i$  and it then returns that the terminal states cannot be reached. If however,  $W_i$  contains one of the terminal states the algorithm terminates and returns that the terminal states can be reached.

The *backward reachability* algorithm in Algorithm 2 is very similar. Since it operates backwards, the set  $W_0$  is initialized with the set of terminal states  $S_f$ . This algorithm terminates when no more states are added to  $W_i$  using  $Pre(W_i)$ , as defined in Equation 2.6. A terminal state is reachable when there is a backwards path reaching one of the initial states in  $S_0$ .

A potential issue of reachability analysis is that termination can only be guaran-

Algorithm 2: Backwards reachability

Input:  $S, S_0, S_f$ Initialization:  $W_0 = S_f, i = 0;$ repeat If  $W_i \cap S_o \neq \emptyset$  then  $W_{i+1} = Pre(W_i) \cup W_i;$ If i = i + 1;Until  $W_i = W_{i-1};$ If  $W_i = W_i = 0$

teed in practice for finite transition system. However, in real-time systems, the number of states is infinite, because continuous time plays a crucial role. Encoding timestamps that are elements of  $\mathbb{R}$  for the events in the systems into states leads to an infinite number of states. Therefore, reachability analysis is in general not guaranteed to terminate.

#### 2.1.3 **BISIMULATION**

The problem of an infinite state space can in some cases be solved by grouping similar states together. A finite state space is obtained if an originally infinite state space can be grouped into a finite number of partitions. A *bisimulation* is a specific similarity relation between two transition systems [Mil8o, Par81]. Two bisimilar systems can have the same model checking properties such as reachability. The goal is to construct a partitioning of a infinite state space into a bisimilar system that has a finite state space.

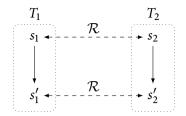

Formally, a bisimulation is a binary relation  $\mathcal{R} \subseteq S_1 \times S_2$  between two transition systems  $T_1 = (S_1, Act_1, \rightarrow, S_{0_1})$  and  $T_2 = (S_2, Act_2, \rightarrow, S_{0_2})$  where:

- (1.) for each  $s_1 \in S_{0_1}$  there exists  $s_2 \in S_{0_2}$  such that  $(s_1, s_2) \in \mathcal{R}$ , and for each  $s_2 \in S_{0_2}$  there exists  $s_1 \in S_{0_1}$  such that  $(s_1, s_2) \in \mathcal{R}$

- (2.) for each pair  $(s_1, s_2) \in \mathcal{R}$

- (2a.) if  $s'_1 \in Post(s_1)$  then there exists  $s'_2 \in Post(s_2)$  with  $(s'_1, s'_2) \in \mathcal{R}$

- (2b.) if  $s'_2 \in Post(s_2)$  then there exists  $s'_1 \in Post(s_1)$  with  $(s'_1, s'_2) \in \mathcal{R}$

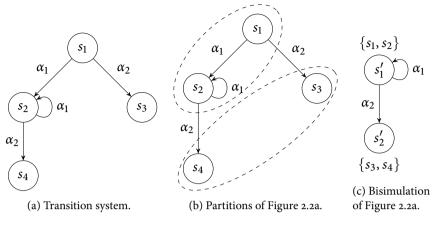

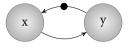

According to (1.) every initial state in  $S_{0_1}$  must be related to an initial state in  $S_{0_2}$  and the other way around. Moreover, the transitions in both systems must be related (2.). For a transition from  $s_1 \in S_1$  to  $s'_1 \in S_1$  there must also exist a matching transition from  $s_2 \in S_2$  to  $s'_2 \in S_2$  such that both  $s'_1$  and  $s'_2$  are related (2a.). Vice versa (2b.), a transition from  $s_2 \in S_2$  must be matched by a transition from  $s_1 \in S_1$ . Figure 2.1 shows this relationship graphically. Multiple states in one transition system can be related to the same state in another transition system.

Figure 2.1: Bisimulation relation for  $T_1$  and  $T_2$ .

A quotient transition system is a partitioning of a transition system T. Partitioning  $\mathcal{P}$  of S contains sets of states from S. Every state in S is included in exactly one partition in  $\mathcal{P}$ . The quotient transition system is defined as  $Q = (\mathcal{P}, Act, \rightarrow, P_0)$  where:

(1.) for all  $P, P' \in \mathcal{P}, P \to P'$  iff  $s \in P$  and  $s' \in P'$  such that  $s \to s'$

$$(2.) P_0 = \{ P \in \mathcal{P} \mid P \cap S_0 \neq \emptyset \}$$

A more strict condition is required for the partitions of *Q* to be a bisimulation of *T*, and thereby retain model checking properties like reachability.

$$\forall P, P' \in \mathcal{P}, \text{ either } P \cap Pre(P') = \emptyset \text{ or } P \cap Pre(P') = P$$

(2.7)

Equation 2.7 states that either none of the state in a partition  $P \in \mathcal{P}$  can transition to a state in a partition  $P' \in \mathcal{P}$ , or all states in P can transition to P'. This particular partitioning groups bisimilar states together. A bisimilar quotient transition system can turn an originally infinite transition system into a finite transition system using the partitions where each partition can be seen as a state in the new transition system.

Figure 2.2a shows an example of a (finite) transition system of which we will derive a smaller bisimilar quotient transition system. The four states of T;  $s_1$ ,  $s_2$ ,  $s_3$  and  $s_4$ , can be partitioned into  $P_1 = \{s_1, s_2\}$  and  $P_2 = \{s_3, s_4\}$  where  $\mathcal{P} = \{P_1, P_2\}$ . It can be verified that this  $\mathcal{P}$  satisfies Equation 2.7. According to this partitioning the transition system in Figure 2.2a is bisimilar to the transition system in Figure 2.2a, although it has only half as many states.

An algorithm that can create such a finite transition system is presented in Algorithm 3 [BKL08]. First, it creates initial partitions for the initial states  $S_0$ , terminal states  $S_f$ , and all remaining states. These partitions are refined until the algorithm terminates exactly when Equation 2.7 is satisfied. During each iteration a pair of sets of states is picked that do not satisfy the bisimulation condition Equation 2.7. These sets are replaced by a set that can transition to  $S_j$ , and another set that cannot transition to  $S_j$ . This process is repeated until all partitions satisfy the bisimulation condition. This algorithm is guaranteed to terminate for finite transition systems.

Figure 2.2: Example of a bisimulation.

Algorithm 3: Automatic derivation of a bisimulation of a finite transition system

Input:  $S, S_0, S_f$ Initialization:  $\mathcal{P} = \{S_0, S_f, S \setminus (S_0 \cup Sf)\};$ while there exists  $S_i, S_j \in \mathcal{P}$  such that  $S_i \cap Pre(S_j) \neq \emptyset$  and  $S_i \cap Pre(S_j) \neq S_i$  do  $S'_i = S_i \cap Pre(S_j);$   $S''_i = S_i \setminus Pre(S_j);$   $\mathcal{P} = (\mathcal{P} \setminus S_i) \cup \{S'_i, S''_i\};$ return  $\mathcal{P}$

For infinite transition systems that include time, termination of the bisimulation algorithm is not guaranteed. Therefore, in the next section we look at timed automata, which are a subset of infinite transition systems for which a finite transition system does exist that is bisimilar to the original transition system.

#### 2.1.4 TIMED AUTOMATA

For real-time systems, not only functional correctness of a system is of interest, but also the temporal behavior of such a system must be within a given specification. In this section we therefore discuss *timed automata* [Lew90, AD90, Dil89, AD94]. Timed automata can be seen as a compromise between expressiveness and analyzability, where the analysis of a timed automaton is always decidable due to restrictions regarding what can be described in the timed automaton. Inherently, including continuous time in a transition system leads to infinite transition systems. However, for timed automata, a finite transition system which is bisimilar to

the originally infinite transition systems can always be constructed.

The beneficial property of timed automata is that a finite transition system can always be constructed, which is a result of the way time can be expressed in a timed automaton. A timed automaton consists of a number of clocks, as real valued variables. All these clocks  $x \in C$  progress time at the same rate  $\dot{x} = 1$ . The only other way the value of a clock can change is when a clock is reset to 0. Each clock can be reset independently. Clocks are therefore useful to measure the time difference between events. Furthermore, constraints on clocks *g* must follow a specific syntax:

$$g ::= x < c \mid x \le c \mid x > c \mid x \ge c \mid g \land g$$

$$(2.8)$$

where  $c \in \mathbb{N}$  and  $x \in C$ , B(C) is the set of allowed clock constraints over *C* according to this syntax. It is crucial for timed automata that all comparisons of clocks are with constant integers. Constraints using rational constants could easily be supported by scaling and shifting these constraints to integers. Without the restrictions on the clock constraints that can be specified, timed automata would in general not be decidable.

A *timed automaton* A is defined as  $A = (L, Act, C, \rightarrow, Inv, l^0)$  where

- » *L* is a finite set of locations

- » Act is a finite set of actions

- » *C* is a finite set of clocks

- » → ⊆  $L \times Act \times B(C) \times 2^C \times L$  is a transition relation

- »  $Inv : L \to B(C)$  is an invariant assignment function

- »  $l^0 \subseteq L$  is a set of initial states

In this definition,  $2^C$  is the power set of *C*, where the number of elements in this power set is  $2^{|C|}$ , where |C| is the number of clocks in *C*. The transition relation consists of  $l \xrightarrow{g:\alpha,D} l'$ , where *g* is a binary clock guard,  $\alpha$  an action in *Act* and  $D \subseteq C$  a set of clocks that is reset to 0. A transition is therefore only possible when the clock constraint of the corresponding guard *g* is satisfied. A transition to another location is atomic and therefore does not advance clocks. A reset to 0 of a clock *x* only occurs when the clock  $x \in D$ . The invariant of a location Inv(l) specifies a upper bound on the value of a clock in that location. This specific location must be left by a transition to another location within the specified bound.

From this definition of a timed automaton, a transition system that also supports time can be constructed. In such a *timed transition system*, the state is not only dependent on the location, but is a tuple (l, n) consisting of both a location  $l \in L$  and value of all clocks n. The transition relation  $\rightarrow$  therefore allows two types of transitions. A transition in a timed transition system is either a discrete or delay transition according to:

(1.) discrete transition:

$$(l, n) \xrightarrow{g:\alpha, D} (l', n)$$

(including clock resets)

(2.) *delay transition*:  $(l, n) \xrightarrow{d} (l, n + d)$  with delay  $d \in \mathbb{R}$  (n + d should satisfy Inv(l))

where the discrete transition (1.) is similar to the one for timed automata. The delay transition (2.) should satisfy the invariant Inv(l) of the current location l, since n + d may not exceed the clock bound of an invariant.

The usage of the continuous time domain for the clocks immediately leads to an infinite state space. Moreover, the time delay *d*, can be infinitly small so there can be an infinite number of delay transitions within a bounded time interval. The transition system of timed automata appears to be infinite. Reachability algorithms for such a system are not guaranteed to terminate. However, based on the clock constraints in Equation 2.8, a limited number of clock regions can be constructed for a timed automaton. A *clock region* is a partitioning of the continuous time space for all clocks where the clock difference inside one region cannot be distinguished using clock constraints, as given in Equation 2.8.

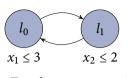

As an example, consider a timed automaton consisting of two clocks  $x_1$  and  $x_2$ , a two locations  $l_0$  and  $l_1$ , and the invariants  $Inv(l_0) = \{x \in \mathbb{R}^2 | x_1 \leq 3\}$  and  $Inv(l_1) = \{x \in \mathbb{R}^2 | x_2 \leq 2\}$ , as shown in Figure 2.3a. For each of the clocks the following clock regions can be identified:

$$x_{1}: x_{1} = 0, x_{1} \in (0,1), x_{1} = 1, x_{1} \in (1,2), x_{1} = 2, x_{1} \in (2,3), x_{1} = 3, x_{1} \in (3,\infty)$$

$$(2.9)$$

$$x_{2}: x_{2} = 0, x_{2} \in (0,1), x_{2} = 1, x_{2} \in (1,2), x_{2} = 2, x_{2} \in (2,\infty)$$

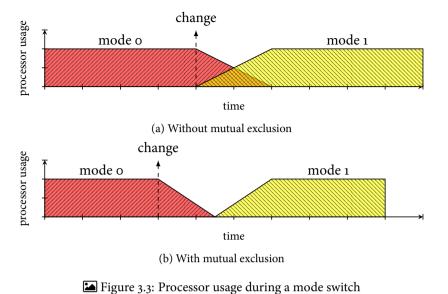

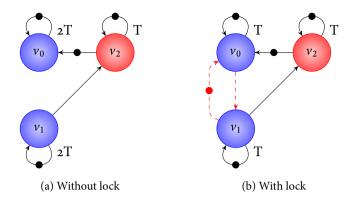

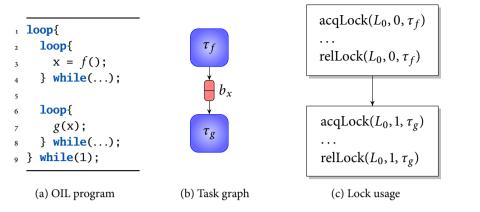

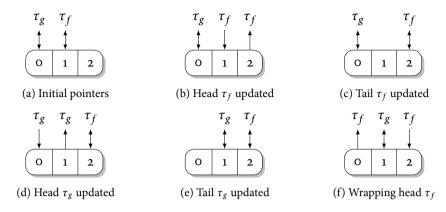

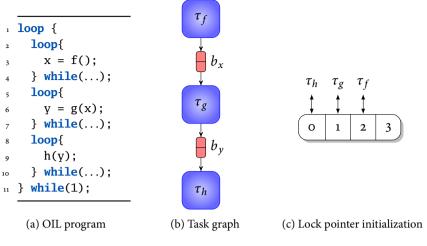

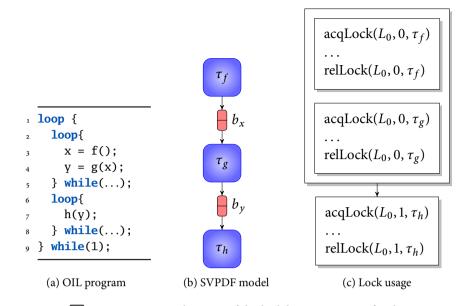

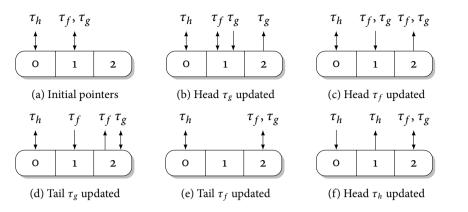

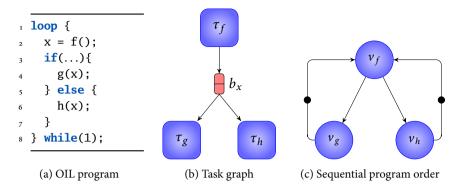

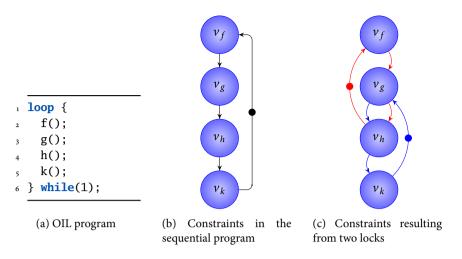

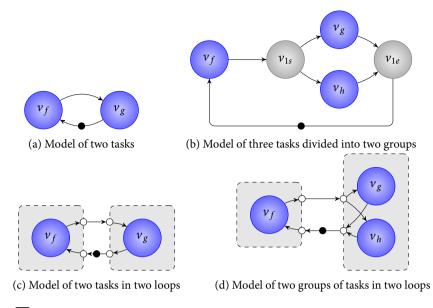

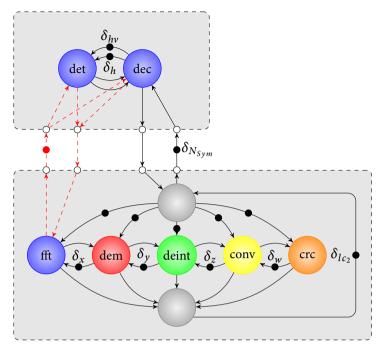

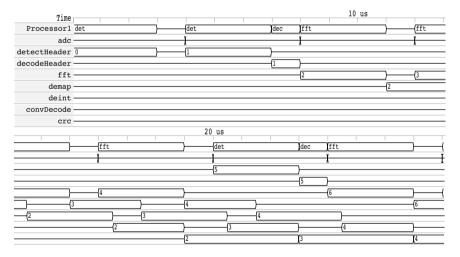

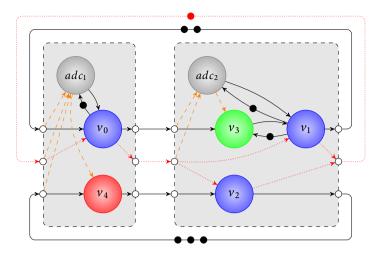

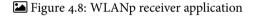

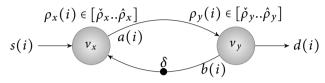

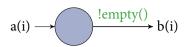

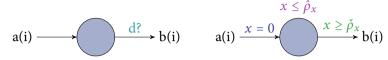

$$(2.10)$$